PIN Diodes, Silicon Strips and GEMs Read-Out Chip

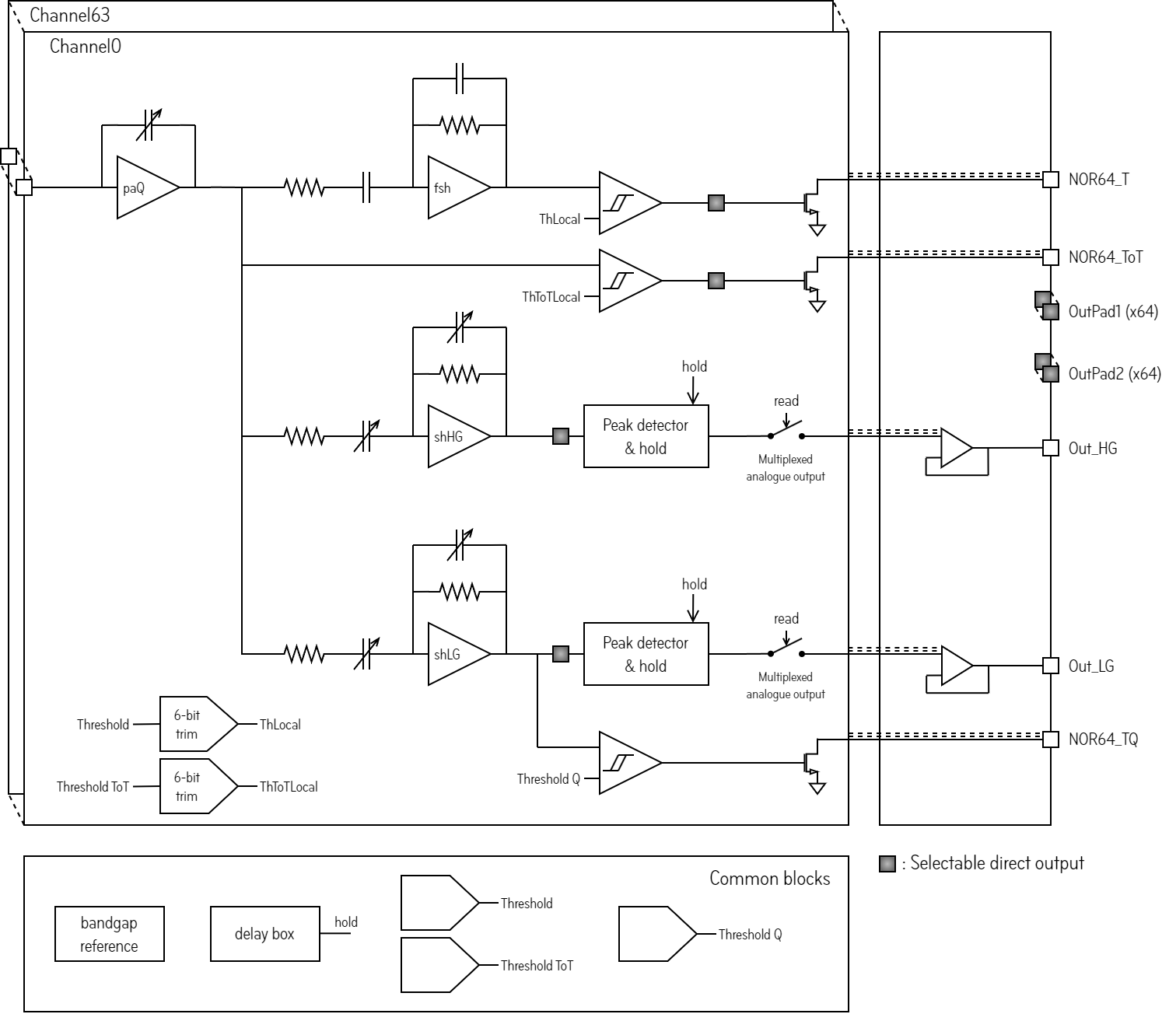

Psiroc is a 64-channel front-end ASIC designed to readout PIN diodes, silicon strips and GEMs, handling detector capacitances ranging from 0 up to few hundreds of pF.

Psiroc allows triggering down to 0.5 fC on sub-20pF detector capacitances and provides dual-gain energy measurement with excellent Signal-to-Noise Ratio on the high gain (SNR over 10 for 0.5 fC) and large dynamic range on the low gain. For input signals over few pC a channel-wise ToT output is also available. Psiroc can be programmed to output the shapers HG/LG, individual triggers or ToT signals (two output pins per channels). The preamplifier gain is adjustable from 125 mV/pC up to 4 V/pC.

Charge measurement is done with peak detectors but those can be used in a track & hold fashion thanks to an internal delay cell. Analog data are outputted on two multiplexed analog output and can be read-out with an external ADC. Shapers shaping time can be adjusted from 20 ns to 3 µs with a step of 20 ns up to 300 ns and a step of 200 ns up to 3 µs. Data acquisition can be done ASIC wide or channel-wise.

Channel-by-channel calibration on the trigger thresholds for time trigger and ToT can be done with individual 6-bit DACs.

| TRL Technology Readiness Level | 4 - ASIC validated in lab environment |

|---|---|

| Available versions |

|

| Detector Read-Out | PIN Diodes, Silicon strips, GEMs |

| Number of Channel | 64 |

| Signal Polarity | Positive, negative |

| Sensitivity | Trigger on 0.5 fC on both polarity |

| Timing Resolution |

< 150 ps RMS @ Qin = 4 fC ; Cd/Cf = 20p/1p (pa gain = 1 V/pC) |

| Dynamic Range | Up to 5 pC with low gain charge measurement and up to 100 pC with ToT |

| Packaging & Dimension |

|

| Power Consumption |

350 mW – Supply voltage : 1.2 V |

| Inputs | 64 analogue inputs |

| Outputs |

|

| Internal Programmable Features |

|

| Evaluation systems |

|

Follow